Hardware

⋮

Rumor

AMD Reportedly Planning Zen 4 EPYC Genoa CPUs With HBM Memory To Tackle Intel Sapphire Rapids Xeons

By

Hassan Mujtaba

Jul 17, 2021 12:38 EDT

Share

Tweet

Submit

Intel may not be the only chip maker to offer HBM powered server CPUs as AMD is reportedly planning its own EPYC Genoa variants based on the Zen 4 architecture for bandwidth-bound workloads.

AMD To Answer Intel's Sapphire Rapids Xeon CPUs With Its Own HBM Powered Zen 4 EPYC Genoa CPUs, Alleges Rumor

The rumor comes from

Inpact-Hardware

who have reportedly received information from their sources that AMD is planning an HBM variant of its upcoming

EPYC Genoa CPUs

powered by the Zen 4 core architecture. While we have learned much about the standard Genoa CPUs, this is the first time we are hearing of an HBM variant.

AMD Ryzen 3 5300G APU Overclocked To 5.5 GHz & Breaks Multiple Quad-Core CPU World Records

According to the report, an EPYC CPU with HBM memory is a recurring question among AMD's partners. Intel has already announced its HBM variant of Sapphire Rapids though those chips

aren't expected around 2023 (in volume)

. AMD is reportedly preparing its

Milan-X

lineup as an intermediate between Zen 3 and Zen 4 which would house 3D chip stacking technology though nothing is clear whether the die stacking is based around CCD's or

V-Cache (similar to next-gen Ryzen Zen 3 Desktop CPUs)

.

It is likely that AMD could offer Milan-X with 3D V-Cache as a showcase of how the low-level cache can help boost performance in bandwidth-bound workloads and ultimately scale it up with more premium HBM options when EPYC Genoa launches. The difference between Milan and Milan-X in terms of launch is around 2-3 quarters and the same timeframe can be expected for an AMD EPYC Genoa lineup with HBM.

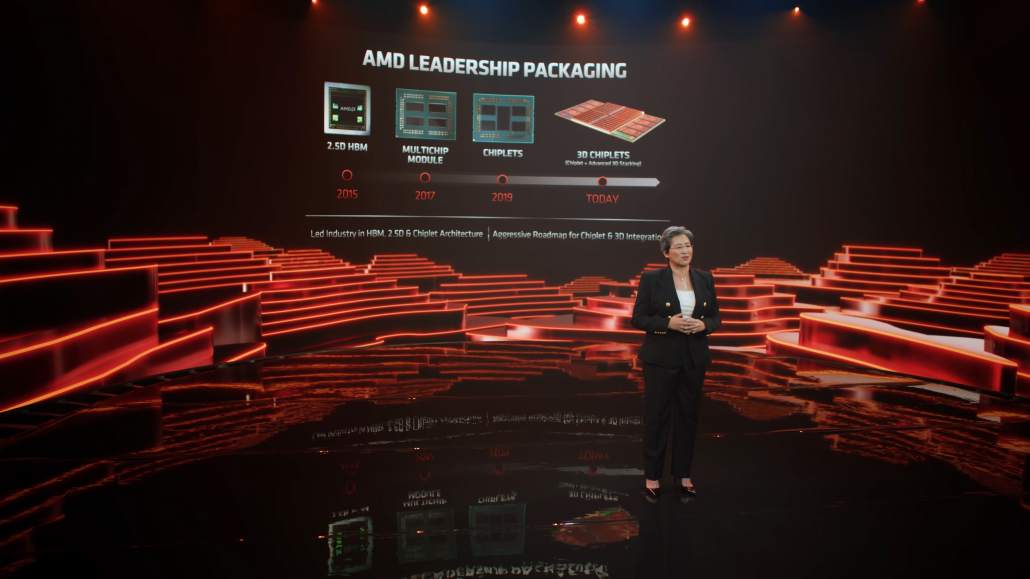

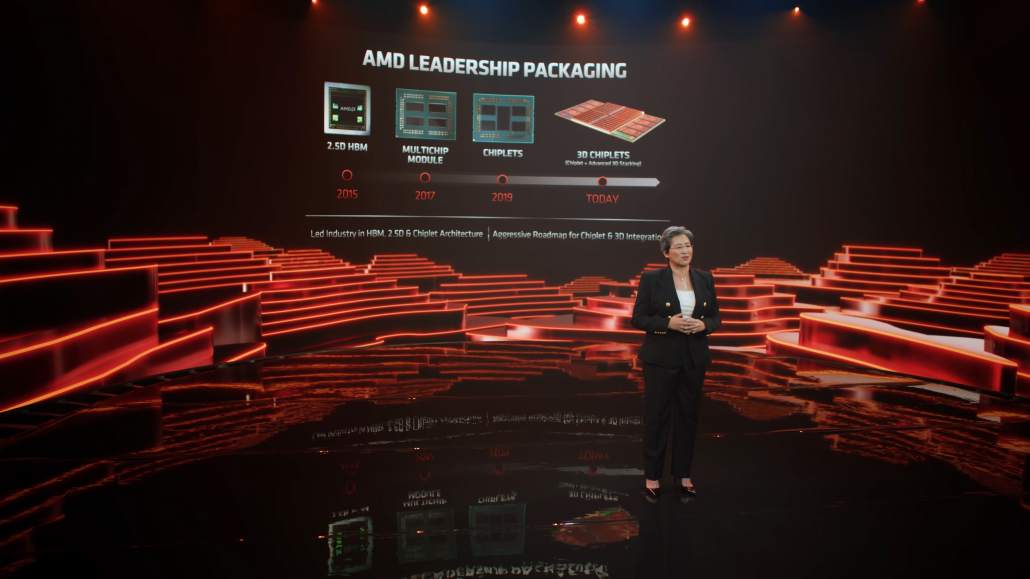

What's definitely going to be interesting is AMD's HBM implementation as they can go with either traditional off-die methods or a more next-gen 3D Chip stacking tech. Intel hasn't confirmed what solution it will use for its HBM integration but they are most likely going to utilize their EMIB and Forveros interconnect/packaging technologies to integrated HBM memory on Xeon CPUs. It will be great to see both companies offer HBM server variants to expand their workload portfolio in the HPC segment.

AMD EPYC CPU Families:

Family Name

AMD EPYC Naples

AMD EPYC Rome

AMD EPYC Milan

AMD EPYC Genoa

Family Branding

EPYC 7001

EPYC 7002

EPYC 7003

EPYC 7004?

Family Launch

2017

2019

2021

2022

CPU Architecture

Zen 1

Zen 2

Zen 3

Zen 4

Process Node

14nm GloFo

7nm TSMC

7nm TSMC

5nm TSMC

Platform Name

SP3

SP3

SP3

SP5

Socket

LGA 4094

LGA 4094

LGA 4094

LGA 6096

Max Core Count

32

64

64

96

Max Thread Count

64

128

128

192

Max L3 Cache

64 MB

256 MB

256 MB

384 MB?

Chiplet Design

4 CCD's (2 CCX's per CCD)

8 CCD's (2 CCX's per CCD) + 1 IOD

8 CCD's (1 CCX per CCD) + 1 IOD

12 CCD's (1 CCX per CCD) + 1 IOD

Memory Support

DDR4-2666

DDR4-3200

DDR4-3200

DDR5-5200

Memory Channels

8 Channel

8 Channel

8 Channel

12 Channel

PCIe Gen Support

64 Gen 3

128 Gen 4

128 Gen 4

128 Gen 5

TDP Range

200W

280W

280W

320W (cTDP 400W)

Share

Tweet

Submit

Stay in the loop

GET A DAILY DIGEST OF LATEST TECHNOLOGY NEWS

Straight to your inbox

Subscribe to our newsletter

Related

Scalpers Selling MSI’s Radeon RX 6600 XT Gaming X Graphics Card For Over $1000 US at Newegg

Hassan Mujtaba

•Aug 7

10

AMD 3D V-Cache Technology In Development for Years, Seen in Ryzen 9 5950X Sample

Jason R. Wilson

•Aug 7

10

AMD Guaranteed To Secure Chinese Approval For Xilinx Deal – Rumor

Ramish Zafar

•Aug 5

10

MSI MEG X570S Unify-X MAX Motherboard Achieves 2.55 GHz FCLK On Air & 2.85 GHz FCLK On LN2 With AMD Ryzen 5000G APU

Hassan Mujtaba

•Aug 5

10

AMD Ryzen 5000G Desktop APUs Now Available For Purchase, 8 Core Ryzen 7 5700G For $359 US & 6 Core Ryzen 5 5600G For $259 US

Hassan Mujtaba

•Aug 5

10

Please enable JavaScript to view the comments.